# The Belle II upgrade

PETTOP

B factories - motivation for upgrade SuperKEB Belle II -detector overview -closer look: PXD The DEPFET sensor -principle & properties -Belle II DEPFET module test beams radiation hardness material gated operation -System aspects Conclusions

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

# B-factory Detectors – a huge success!

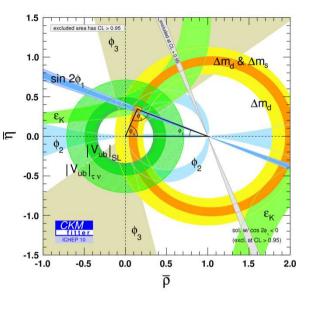

- Measurements of CKM matrix elements and angles of the unitarity triangle

- » Observation of direct CP violation in B decays

- >> Measurements of rare decays (e.g.,  $B \rightarrow \tau v$ ,  $D \tau v$ )

- » b→s transitions: probe for new sources of CPV and constraints from the b→sγ branching fraction

- ➤ Forward-backward asymmetry (A<sub>FB</sub>) in b→sll has become a powerfull tool to search for physics beyond SM.

- » Observation of D mixing

- » Searches for rare  $\tau$  decays

- » Observation of new hadrons

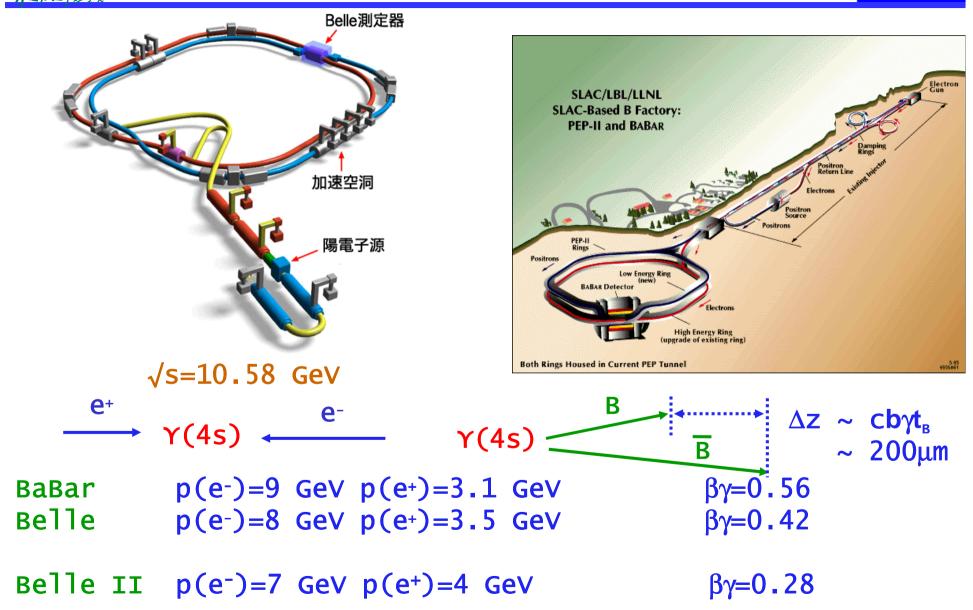

# **Asymmetric B factories**

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

An. Dozt

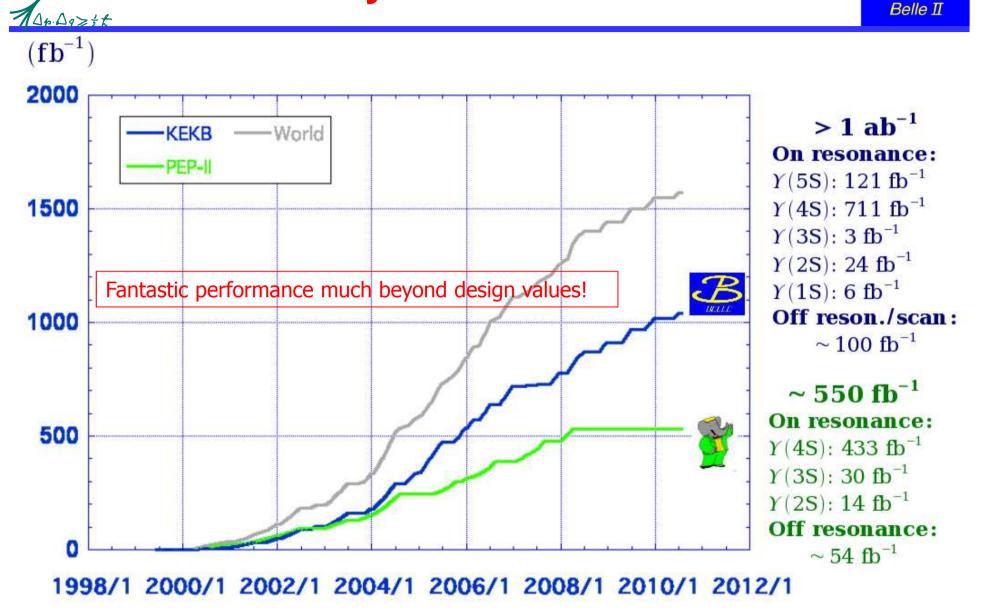

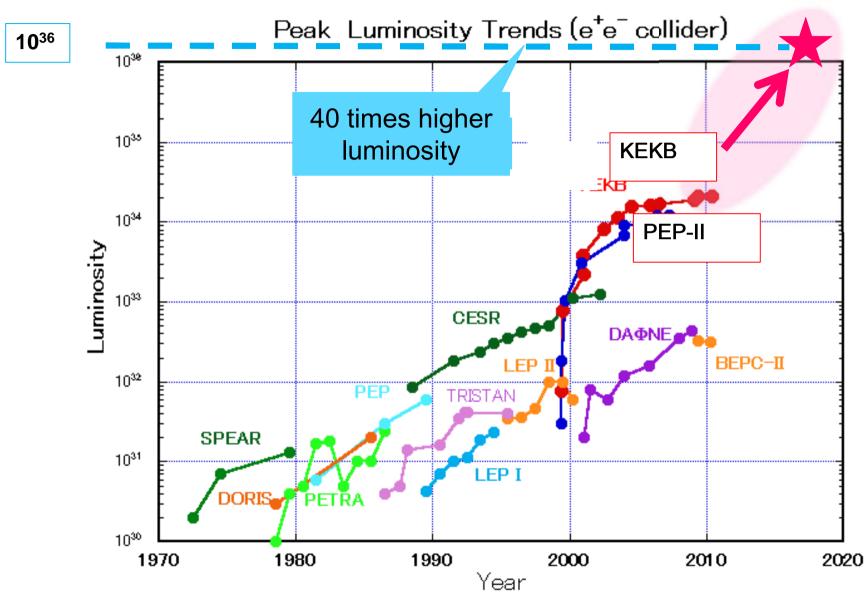

# Luminosity at the B Factories

### Last KEKB beam abort: June 30, 2010

First physics run on June 2, 1999 Last physics run on June 30, 2010  $L_{peak} = 2.1 \times 10^{34} / cm^2 / s$ L > 1ab<sup>-1</sup>

H.-G. Moser, Join Instrumentaton Seminar, Hamburg, Jan. 18, 2013

# **Nobel Prize in Physics 2008**

Confirmation by Babar and Belle

# Are we done yet ?

# **Motivation for Upgrade**

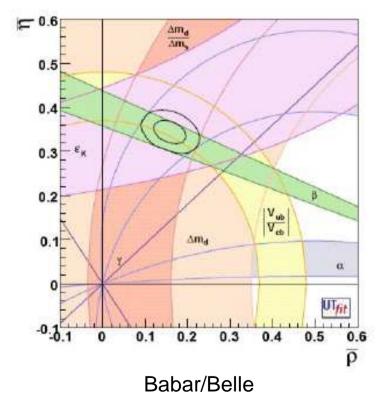

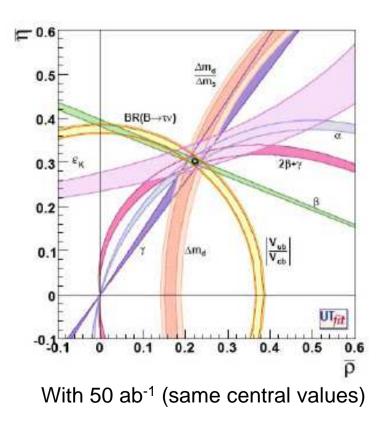

Measure CKM elements as precisely as possible Overconstrain unitarity triangle Look for deviations from SM

$$\begin{split} \Phi_1 / \beta &= (21.\pm 1 \ 0.9)^{\circ} \\ \Phi_2 / \alpha &= (88.4 \ \pm 5.6)^{\circ} \\ \Phi_3 / \gamma &= (70 \ \pm 29)^{\circ} \end{split}$$

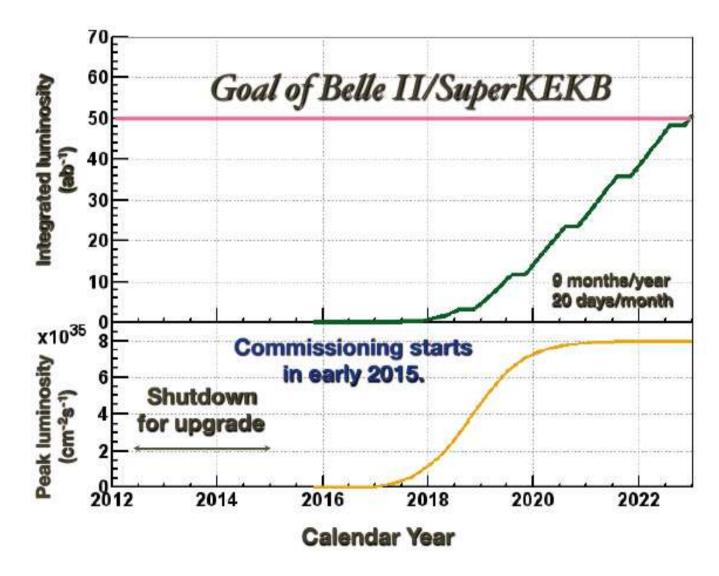

=> Need about 50 ab<sup>-1</sup>

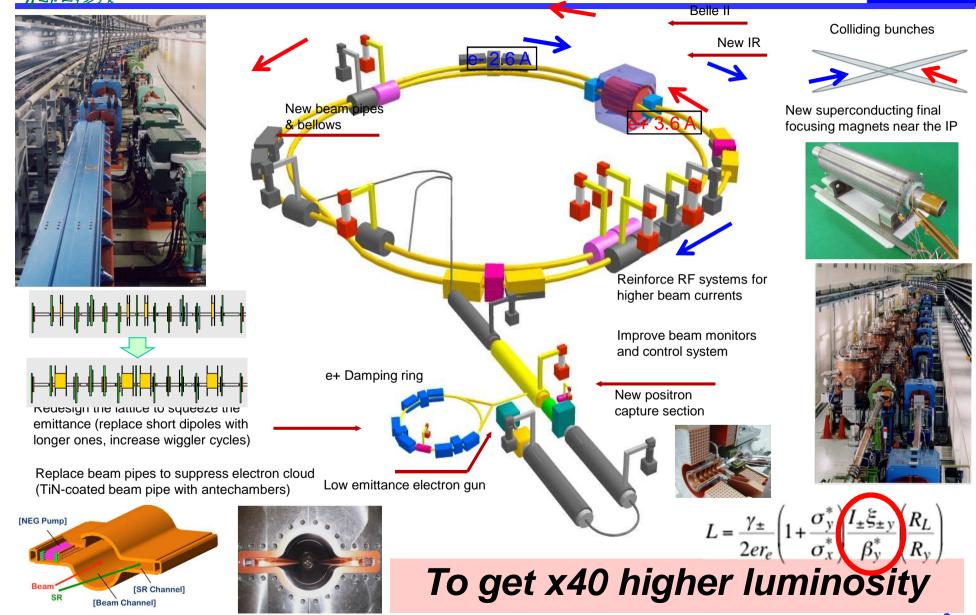

# **KEKB to SuperKEKB**

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

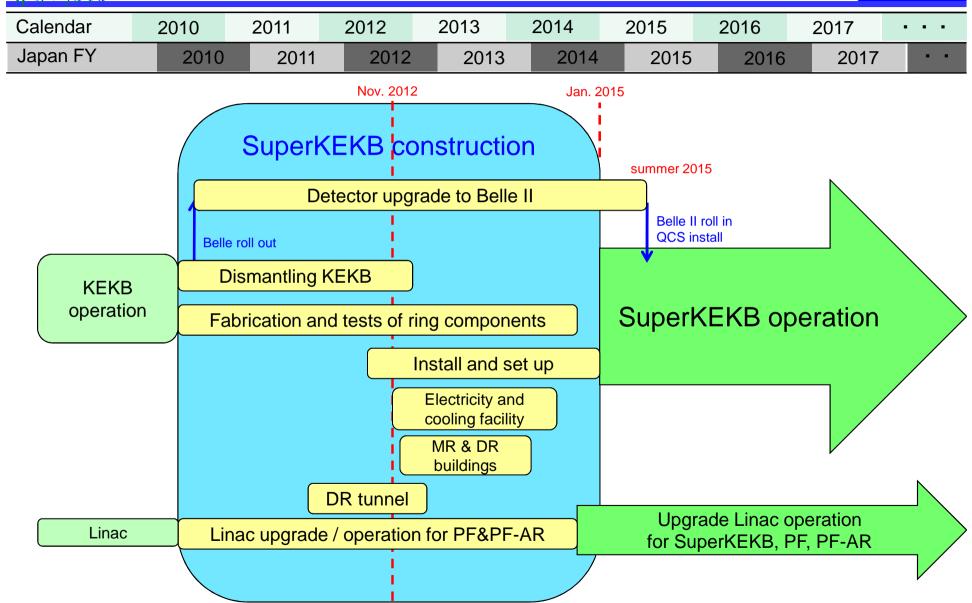

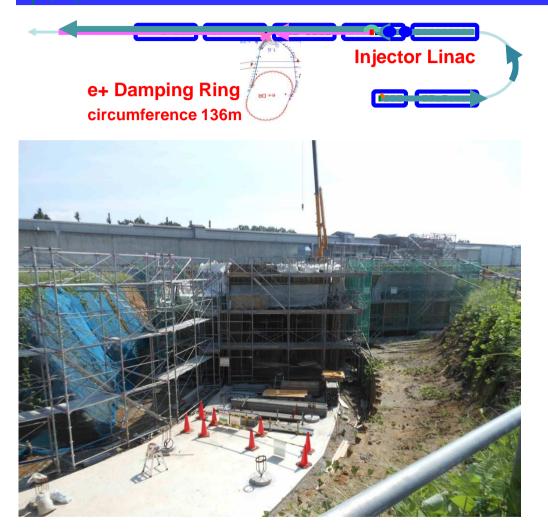

# **SuperKEKB Schedule**

Tunnel construction for new bending ring

beam pipes after baking and TiN coating. They are temporary stocked until moved to tunnel

100 new bending pipes are installed

#### Machine upgrade on schedule

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

H.-G. Moser, Join Instrumentaton Seminar, Hamburg, Jan. 18, 2013

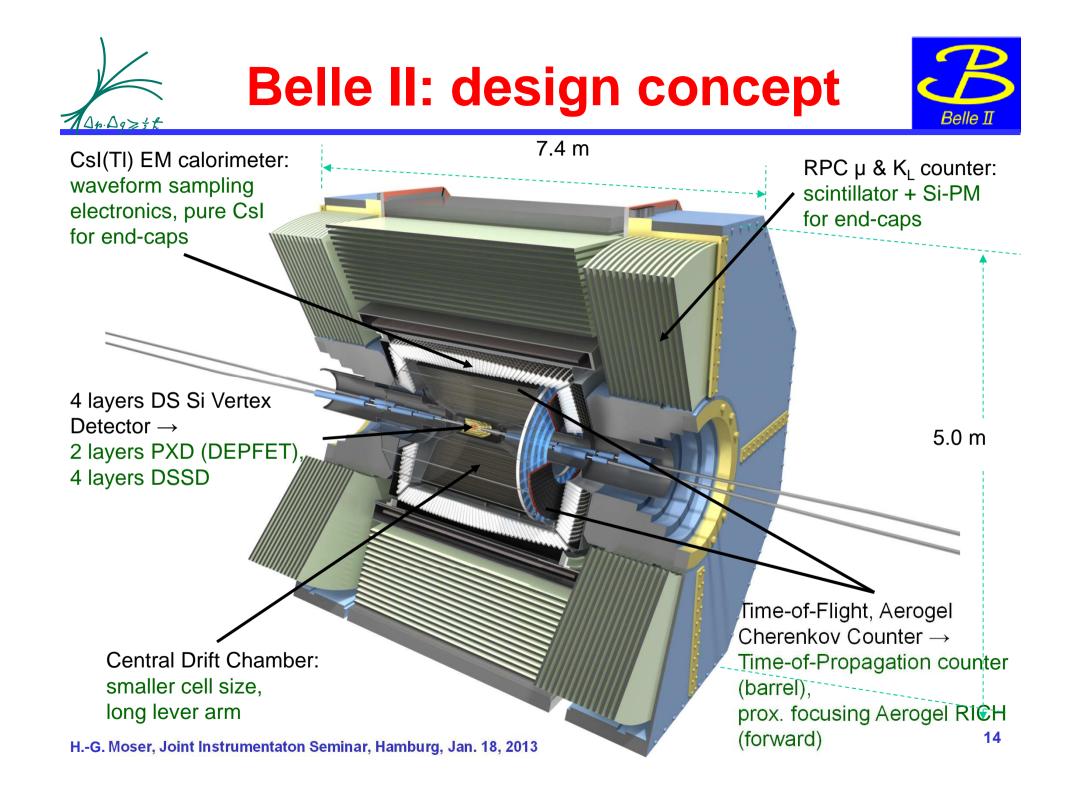

# Requirements for the Belle II detector

#### Critical issues at L= 8 x 10<sup>35</sup>/cm<sup>2</sup>/sec

Higher background (×10-20)

radiation damage and occupancy

fake hits and pile-up noise in the EM Calorimeter

Higher event rate ( ×10)

- higher rate trigger, DAQ and computing

Special features required

--  $\gamma\beta$  reduced by a factor of 2: compensated by improved vertexing

Result: significant upgrade

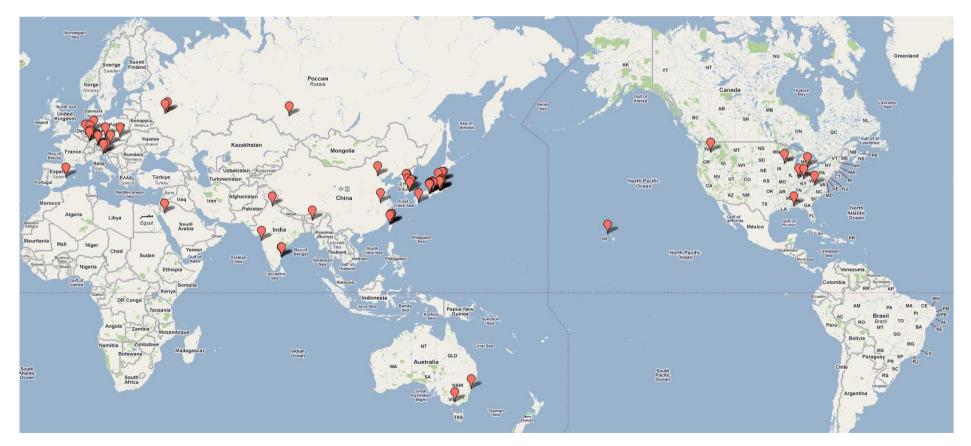

# **Belle II Collaboration**

15 countries, ~60 institutions (9 German)

#### ~400 collaborators

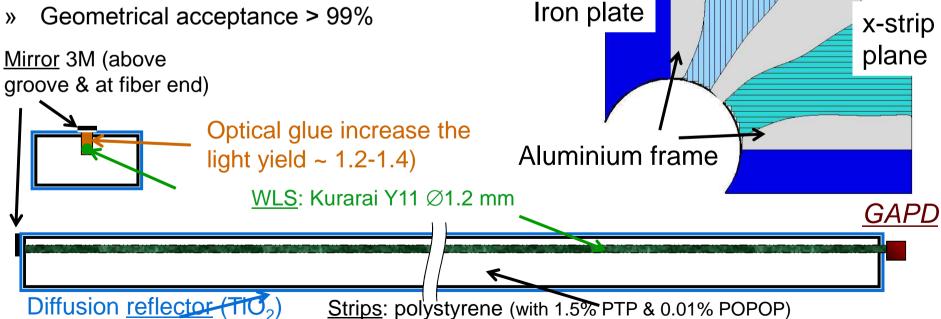

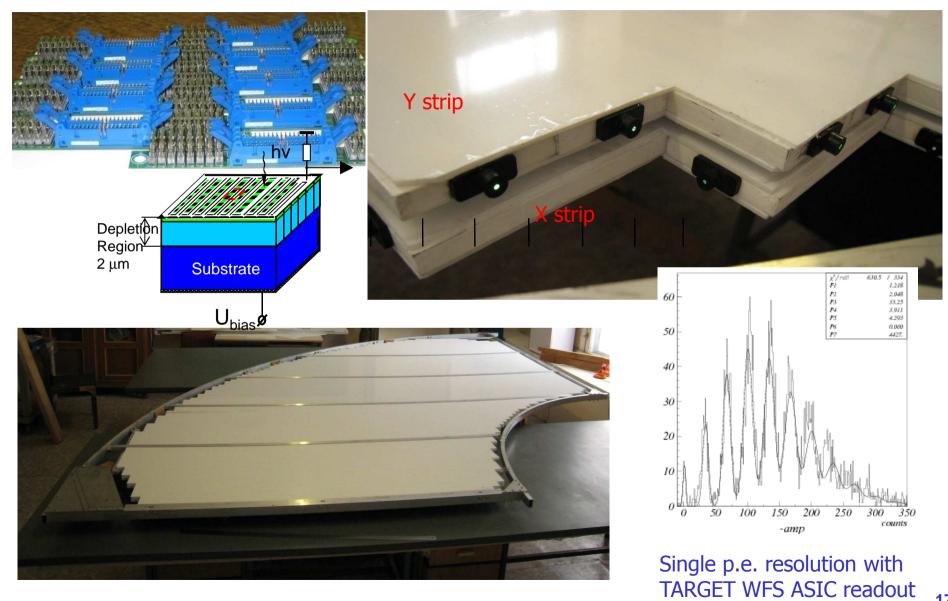

# Endcap KLM upgrade

y-strip

plane

Replace RPCs with Scintillator-based approach

- Two independent (x and y) layers per superlayer made of orthogonal **》** strips with WLS read out

- Photo-detector = avalanche photodiode in Geiger mode (SiPM) »

- ~150 strips in one 90° sector **》** (max L=280cm, w=25mm)

- ~16800 read out channels »

- Geometrical acceptance > 99% »

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

# Endcap KLM upgrade

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

$\Delta p \cdot \Delta q \geq \frac{1}{2} t$

17

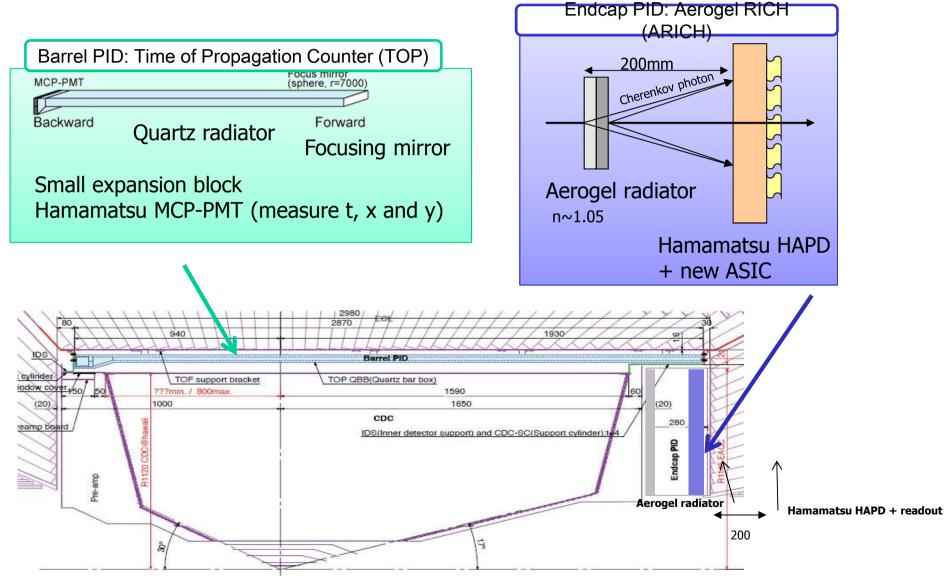

# **Particle Identification**

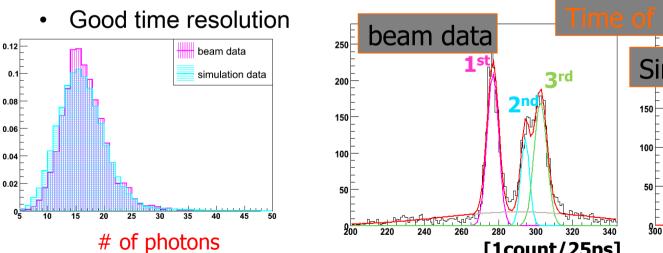

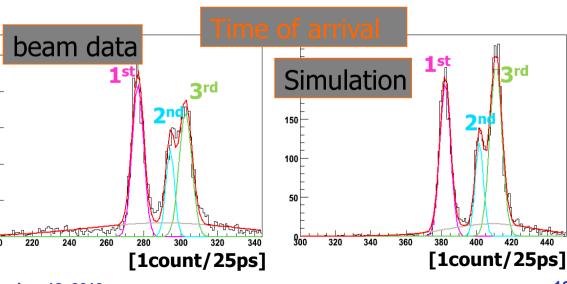

# **TOP (Barrel PID)**

SL10 MCP-PMT

- » Quartz radiator

- 2.6m<sup>L</sup> x 45cm<sup>W</sup> x 2cm<sup>T</sup>

- Excellent surface accuracy

- » MCP-PMT

- Hamamatsu 16ch MCP-PMT

- Good TTS (<35ps) & lifetime

- Multialkali photo-cathode → SBA

- » Beam test in 2009

- # of photons consistent

quartz Beam spot 915mm 875mm 1st

H.-G. Moser, Join Instrumentaton Seminar, Hamburg, Jan. 18, 2013

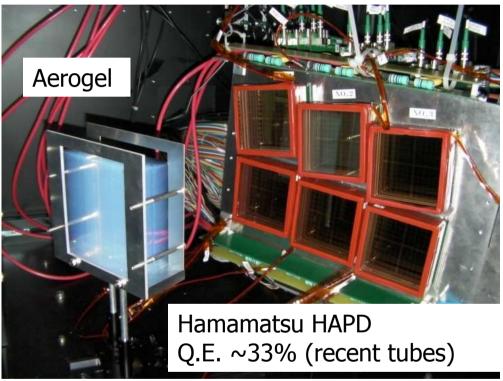

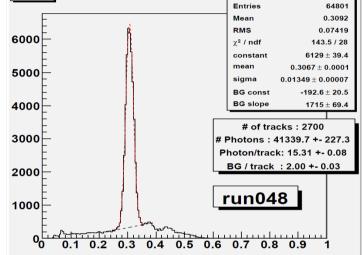

# **Aerogel RICH (endcap PID)**

ahistmiki

#### Test Beam setup

An Agzi

#### **6.6 σ** p/K at 4GeV/c !

Cherenkov angle distribution

ahist

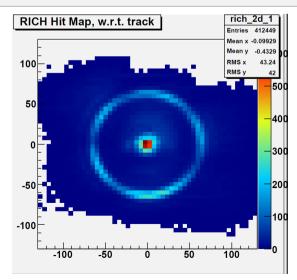

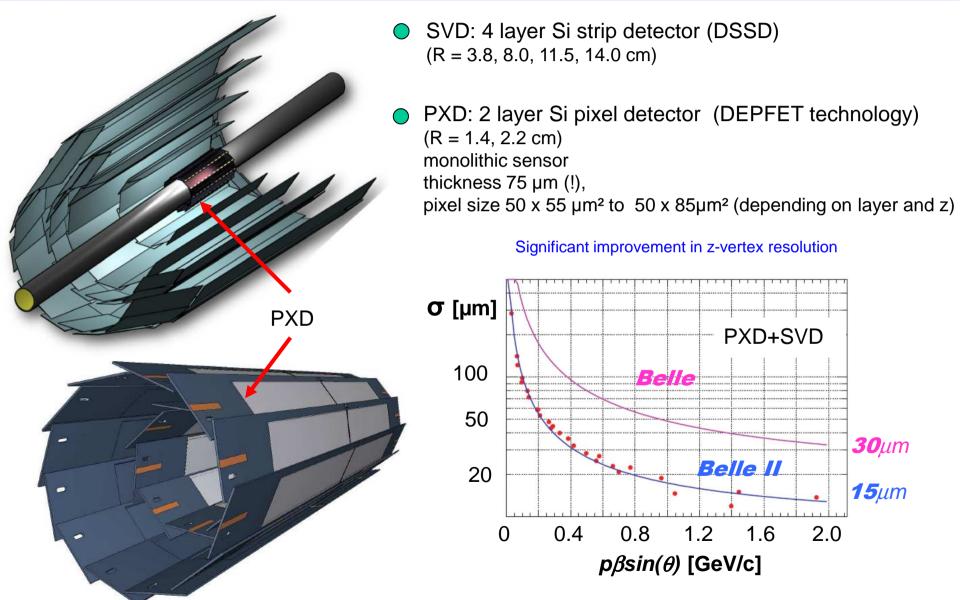

### Silicon Tracking System @ Belle II

H.-G. moser, Joint Instrumentation Seminar, mampurg, Jan. 18, 2013

# Silicon Vertex Detector

H.-G. Moser, Join Instrumentaton Seminar, Hamburg, Jan. 18, 2013

mpi Ibletterlabor

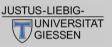

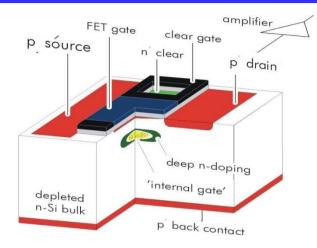

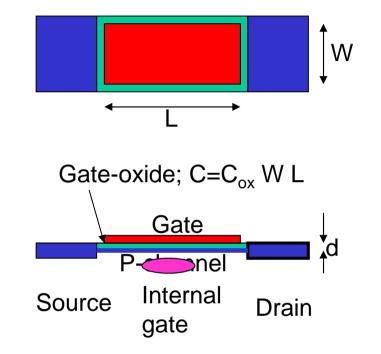

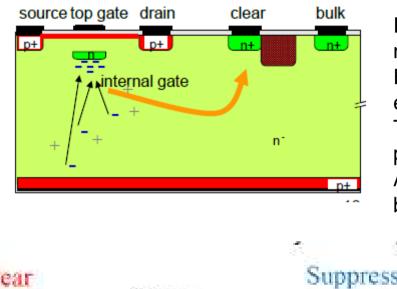

Each pixel is a p-channel FET on a completely depleted bulk

A deep n-implant creates a potential minimum for electrons under the gate ("internal gate")

Signal electrons accumulate in the internal gate and modulate the transistor current ( $g_q \sim 400 \text{ pA/e}^{-}$ )

Accumulated charge can be removed by a clear contact ("reset")

Fully depleted:  $\Rightarrow$  large signal, fast signal collection

Low capacitance, internal amplification: => low noise

High S/N even for thin sensors

Rolling shutter mode (column parallel) for matrix operation  $\Rightarrow$  20 µs frame readout time

=> Low power (only few lines powered),

### How does it work?

A charge q in the internal gate influences a mirror charge  $\alpha$ q in the channel ( $\alpha$  <1, for stray capacitance) This mirror charge is equivalent to a change of the gate voltage:

$$\Delta V = \alpha \text{ q } / \text{ C} = \alpha \text{ q } / (\text{C}_{\text{ox}} \text{ W L})$$

FET in saturation:

$$I_{d} = \frac{W}{2L} \neq \mathcal{U}_{2L}^{W} \left( \mathcal{U}_{Oax}^{G} + \left( \frac{\mathcal{O}_{Q_{s}}}{C_{Oax}^{G}} WL^{h} \right)^{2} V_{h} \right)^{2}$$

$$\label{eq:l_d:source-drain current} \begin{split} I_d: & \text{source-drain current} \\ C_{\text{ox}}: & \text{sheet capacitance of gate oxide} \\ \mu: & \text{mobility (p-channel: holes)} \\ V_g: & \text{gate voltage} \\ V_{\text{th}}: & \text{threshold voltage} \end{split}$$

#### Chavesision duataonce:

$$g_{q} = \frac{\exists I_{d} \mathcal{A}_{d} \mathcal{A}_{d} \mathcal{A}_{G}}{dq_{s}} \frac{\mathcal{W}}{G_{L^{2}}} \left( \mathcal{W}_{G} + \frac{\mathcal{O}_{o} \mathcal{A}_{sG}}{C_{os} WL} - \mathcal{V}_{th}^{th} \right) = \alpha \sqrt{2 \frac{I_{d} \mu}{L^{3} W C_{os}}}$$

$$g_{q} = \alpha \sqrt{\frac{2 \frac{\mathcal{W} \mu C_{os} I_{d}}{C_{os} WL} - \mathcal{O}_{th}}{WL C_{os} L}} \frac{g_{m}}{C}$$

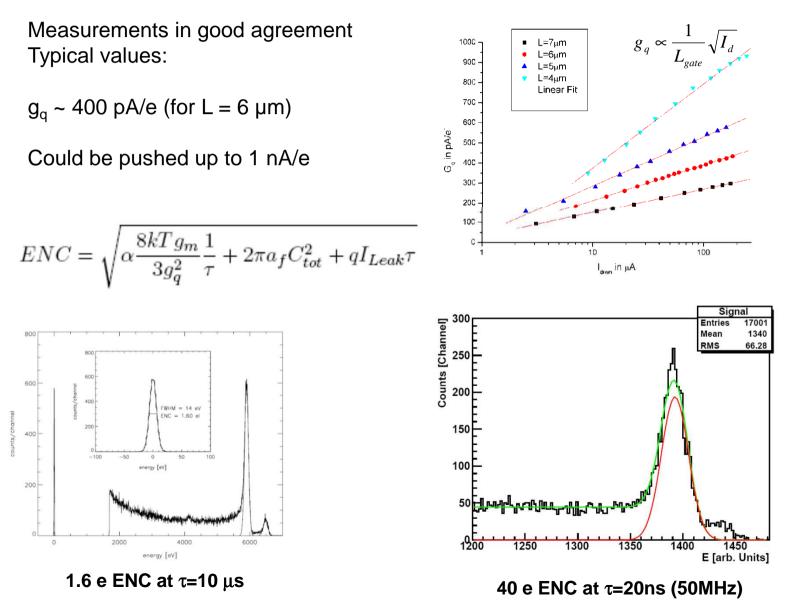

# **Gain and Noise**

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

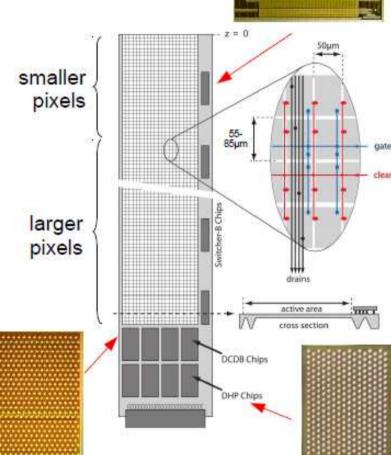

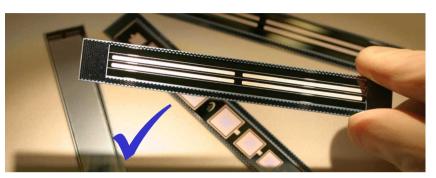

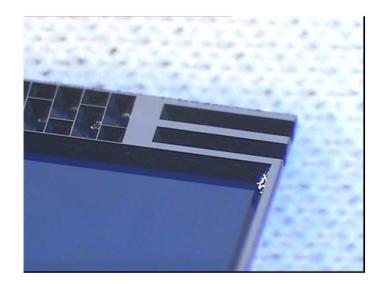

# **Sensor Module/Ladder**

- PXD ladder is built of two half modules

- module length restricted by wafer size

- yield considerations

| Half<br>Module      | Inner<br>layer         | Outer<br>layer                                 |

|---------------------|------------------------|------------------------------------------------|

| # (half)<br>modules | 8 (16)                 | 12 (24)                                        |

| Radius              | <mark>14 m</mark> m    | 22 mm                                          |

| Pixel<br>size       | 50x55 μm²<br>50x60 μm² | 50x70 μm <sup>2</sup><br>50x85 μm <sup>2</sup> |

| Thick<br>ness       | 75 µm                  | 75 µm                                          |

| #<br>pixels         | 1536(z) x<br>250(R-ф)  | 1536(z) x<br>250(R-ф)                          |

| Size                | 15x68 mm <sup>2</sup>  | 15x85 mm <sup>2</sup>                          |

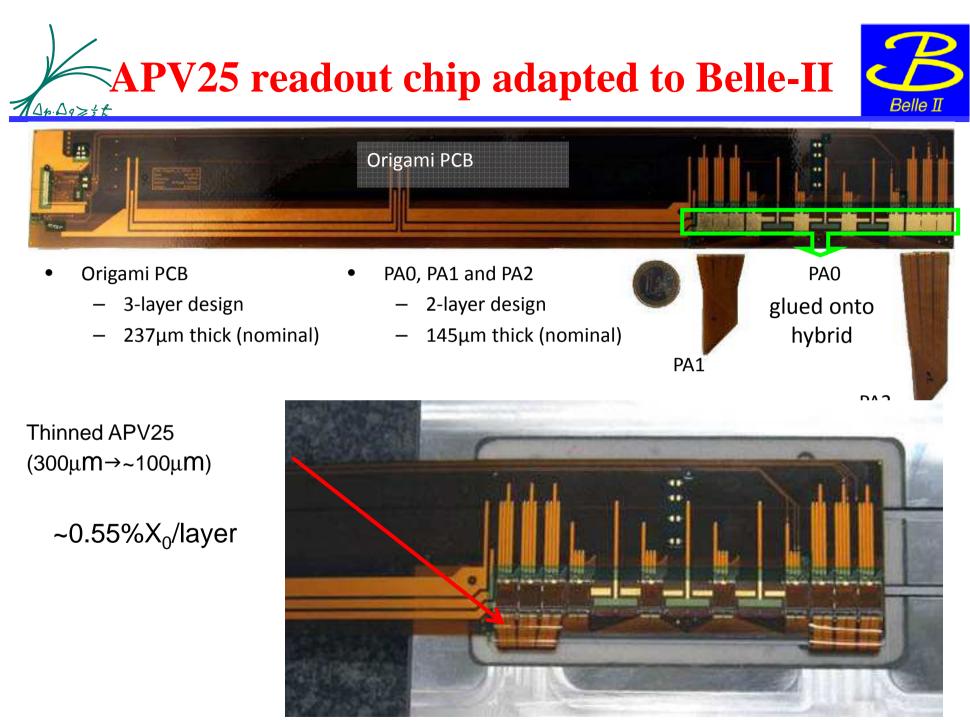

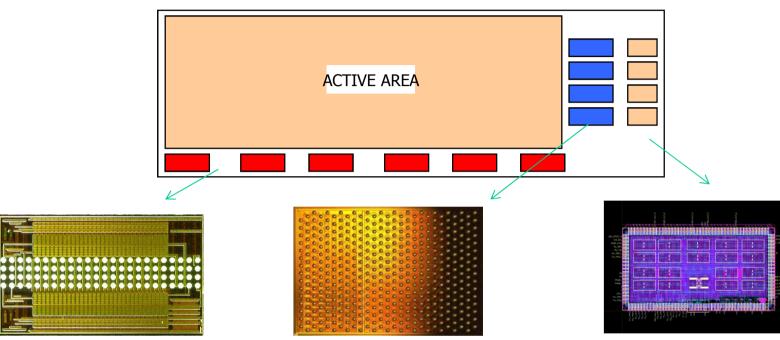

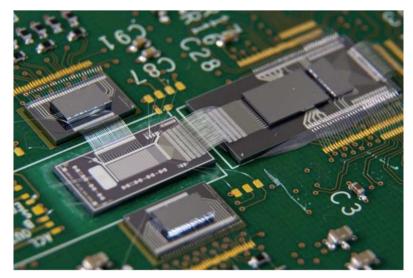

# **ASICs for control and readout**

#### Switcher

An Agzi

Control of gate and clear 32 x 2 channels Switches up to 30V AMS 0.18 µm HV technology Tested up to 36 Mrad

#### DCDB

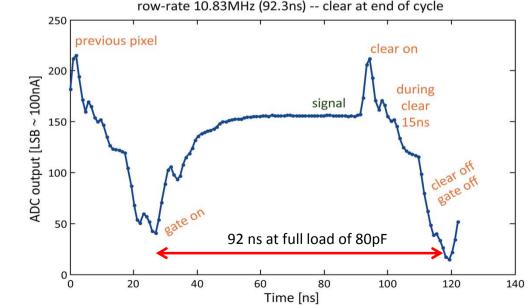

Amplification and digitization of DEPFET signals 256 input channels 8-bit ADC per channel 92 ns sampling time UMC 189nm Rad hard design

#### DHP

Signal processor Common mode correction Pedestal subtraction 0-supression Timing and trigger control IBM 90 nm Rad hard design Convert to TSMC 65nm

All three chips fabricated and tested

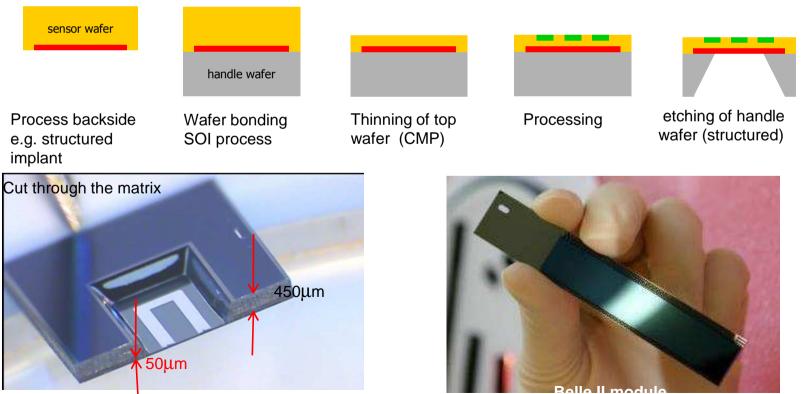

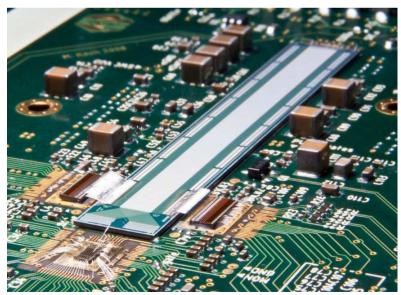

# **Sensor Thinning**

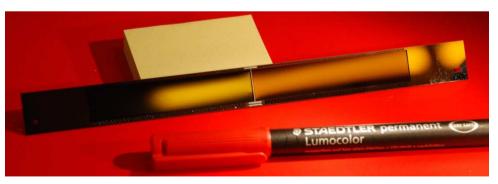

#### Need thin (50µm-75µm) self supporting all silicon module

H.-G. Moser, Joint Instrumentation Seminar, Hamburg, Jan. 18, 2013

- » v-grooves in support silicon

- » butt-joint between two half-ladders

- » reinforced with 3 ceramic inserts

- » 2x300µm dead area per ladder

- » mechanical tests  $\rightarrow$  remarkably robust!!

- » bowing: up to 1 mm sag (over 10 cm)

- » tension: 40 to 60 N, then the Si broke

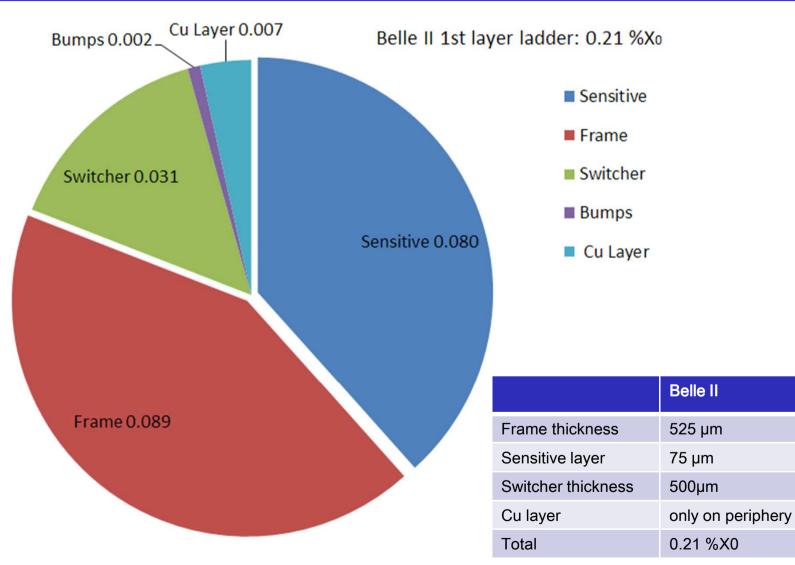

#### All-silicon module – material budget (single layer)

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

# **PXD6 testing in the lab**

- >> bench tests in the lab

- → determine best operating point (Clear, ClearGate, Drift..)

- └→ in-pixel studies with laser

- └→ radioactive source tests

- └→ read-out speed...

- >> goal @Belle II

- ≫ 320 MHz system clock

- > 50 kHz frame rate (20µs r/o time per frame)

- ≫ 768 rows, 4-fold r/o  $\rightarrow$  ~100 ns per row

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

single pixel DEPFET (COCG LE) current output as seen by DCD row-rate 10.83MHz (92.3ns) -- clear at end of cycle

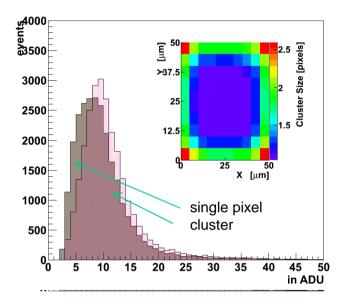

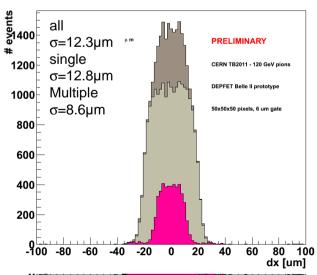

### **Test Beam**

Test beam at CERN, October 2011

| a) | PXD6, 50µm, L=4µm, standard ox: |  |

|----|---------------------------------|--|

|----|---------------------------------|--|

b) PXD6, 50 $\mu$ m, L=6 $\mu$ m, thin ox:

S/N ~ 40 S/N ~ 20

- thin oxide not yet optimized => smaller S/N DCD V1 does not allow optimal Idrain final sensors are 50% thicker

#### => S/N > 40 expected for optimal settings

Readout speed up to 320 MHz (100ns readout time)

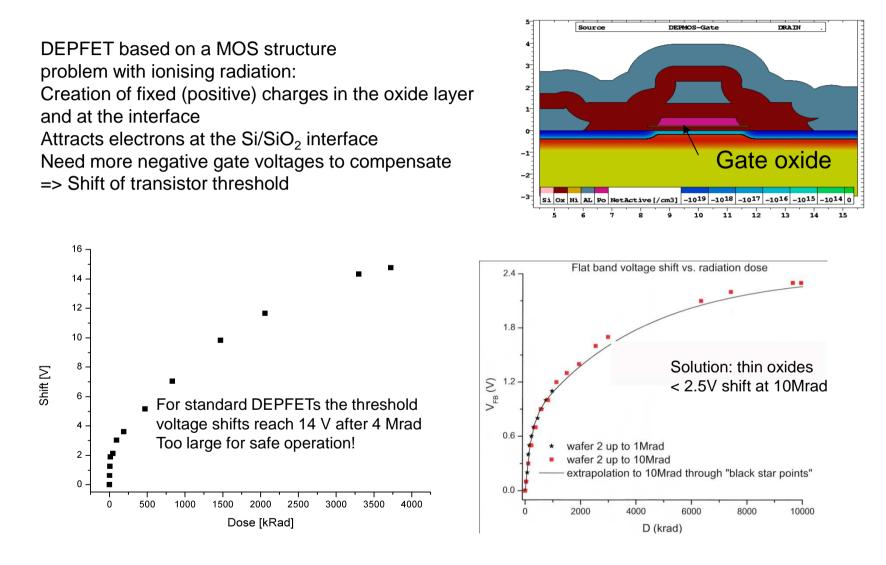

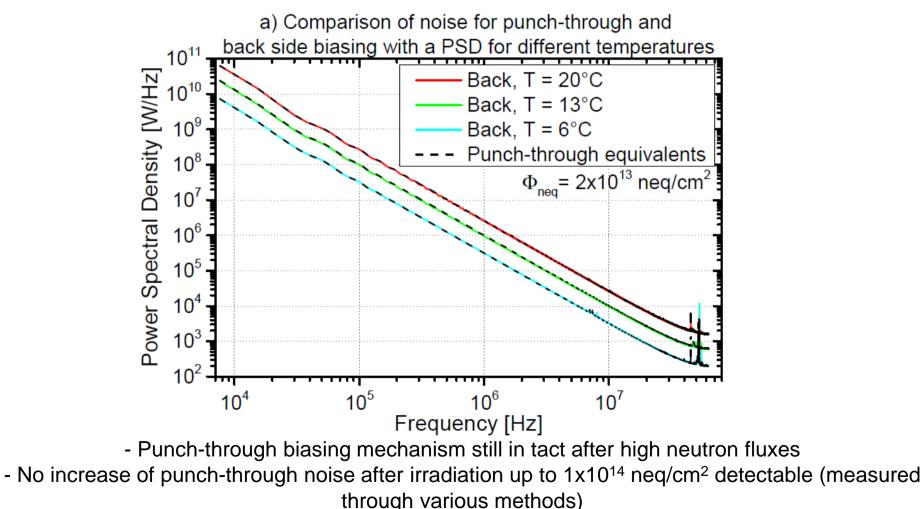

# **Radiation Hardness**

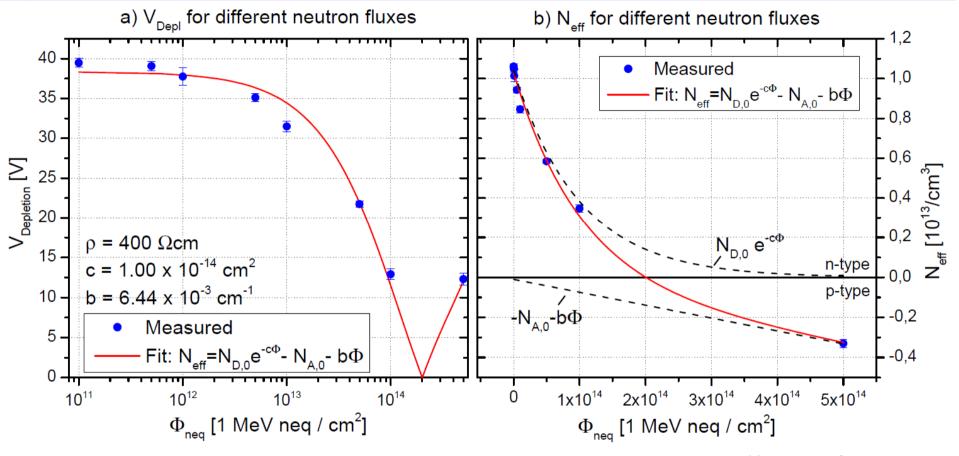

# **Neutron irradiations**

Type Inversion at an equivalent neutron flux of approximately 2x10<sup>14</sup> neq/cm<sup>2</sup>

→ No Type Inversion expected during BELLE II operations

- Measured leakage current after a neutron flux of 2x10<sup>14</sup> neq/cm<sup>2</sup> was roughly 6x10<sup>-4</sup> A/cm<sup>3</sup>

# **Punch Through Bias**

Punch through mechanism allows to bias the backside from a contact on the front side. No electrical connections on backside needed

However, CDF observed excess noise in punch through biased strip detectors

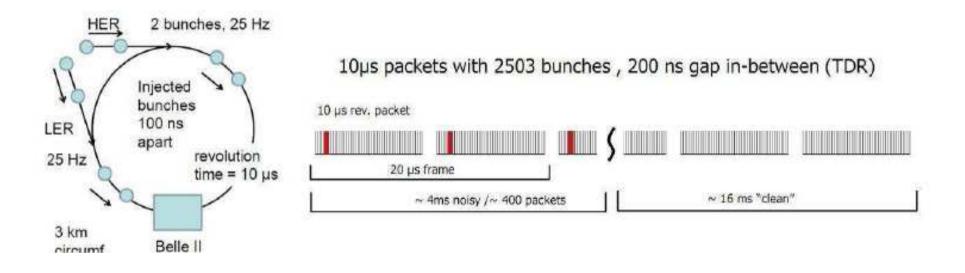

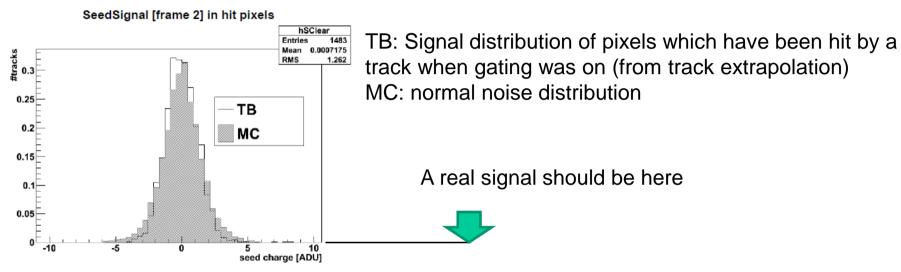

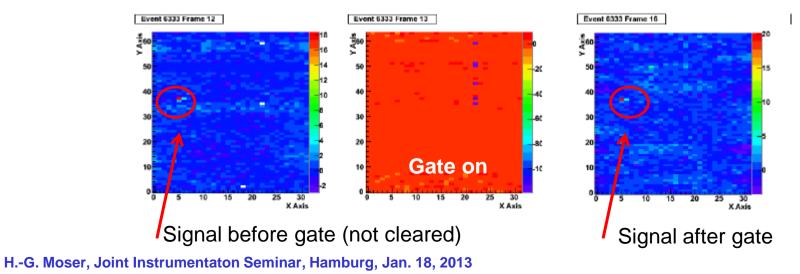

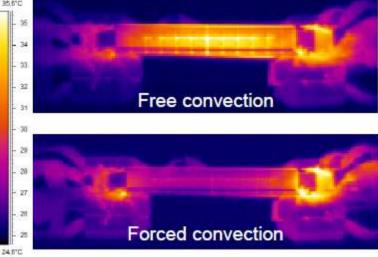

# **Injection Noise & Gating**

Sensor filled with hits from freshly injected bunches = ~ 20% dead time

Gating : Sensor is made blind for a short time during high background (noisy bunch) Signals detected in the clean period before are preserved

Simulations, lab tests with lasers and particle beams demonstrate feasibility of gating

h. Do>t

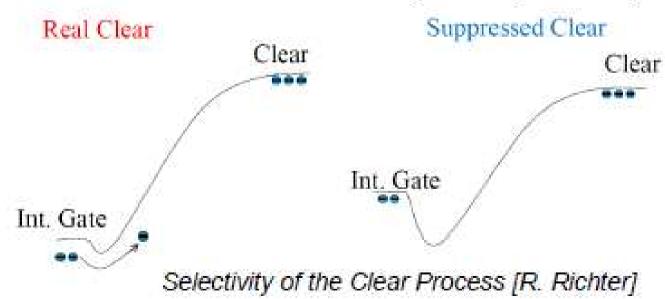

#### **Gated Operation**

In normal clear operation the gate is pulsed negatively (repells electrons) The clear is pulsed positively (attracts electrons from internal gate and bulk underneath)

In gated mode the gate is not pulsed, Remains attractive for electrons The clear is pulsed positively, Attracte electrons fro, bulk underneath

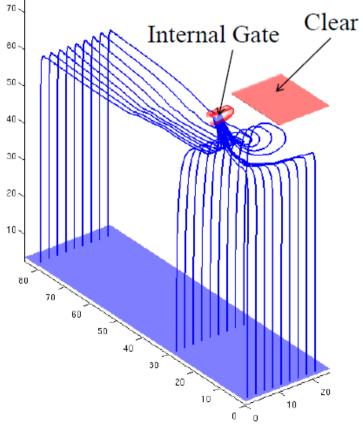

### **Electron drift directions**

70-

60-

50

40

Normal operation: Signal charge drifts into internal gate

Gated Mode Charges from background drift directly to clear gate

Signal already stored in internal gate is protected

- good for electron dumping

IG

Huge clear region compared to Internal Gate

Clear = 18V

#### Lab test with laser

ADUs in blindphase: 70722

ClearHigh

6000

5000

4000

3000

200

1000

-1000

ADU

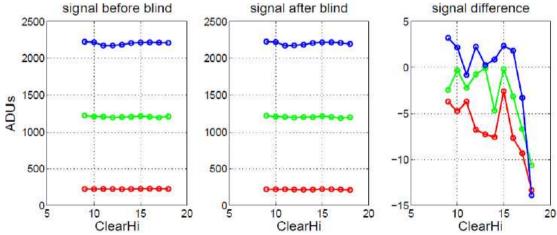

Inject (using a laser) 180k electrons (MIP: 6k electrons)

scan clear voltage => 12V needed for complete shield

$6 \Delta a > 4$

Test storage capacity during gating Measure injected signal before and after gate

=> No losses up to 14V clear voltage

three different amounts of electrons have been created (red, green, blue curve)

shielding of the internal gate works for all studied ClearHi voltages

-0.5V ClearGate -1.0V ClearGate

-1.5V ClearGate -2.0V ClearGate -2.5V ClearGate

-3.0V ClearGate

-4.0V ClearGate

-

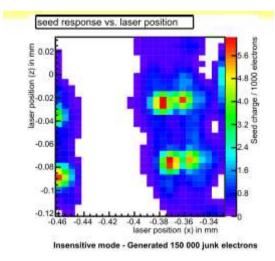

#### **Tests with beam**

Gated mode successfully tested in the lab (laser) and test beam

Protection: the signal of a real hit is still present after gating:

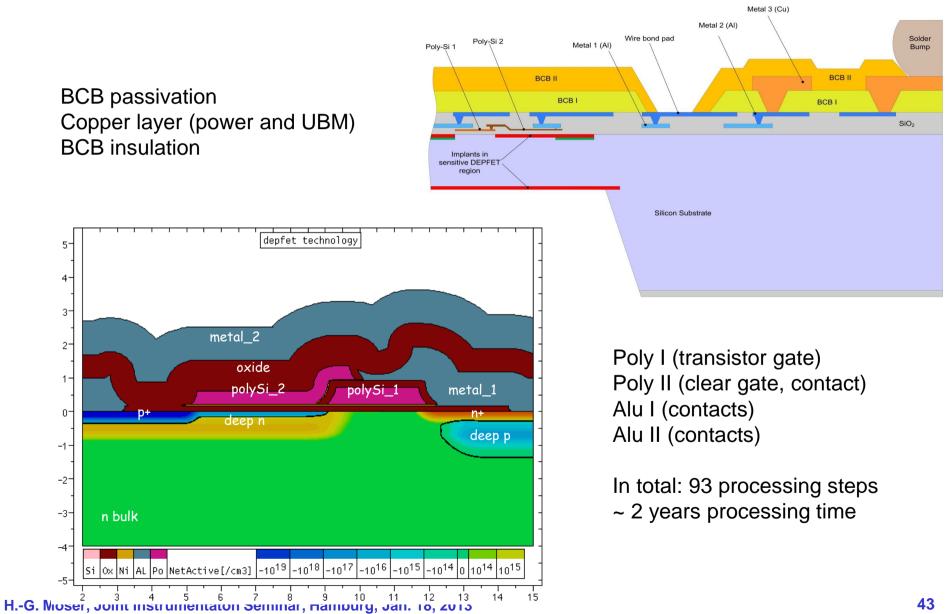

#### **Production Facilities**

800m<sup>2</sup> cleanroom Class 1 <u>6" production line</u>

Thermal oxidation Photolithography (double sided, mask and laser writer) (double sided, mask and laser writer) Wet chemical etching Ion implantation LTO Nitride Polysilicon Al-sputtering

# **DEPFET** production

h. Do>+;

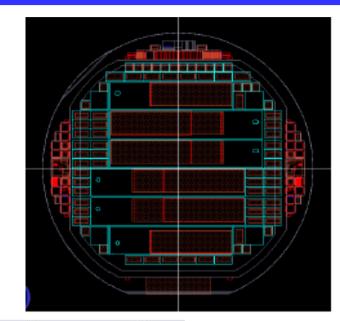

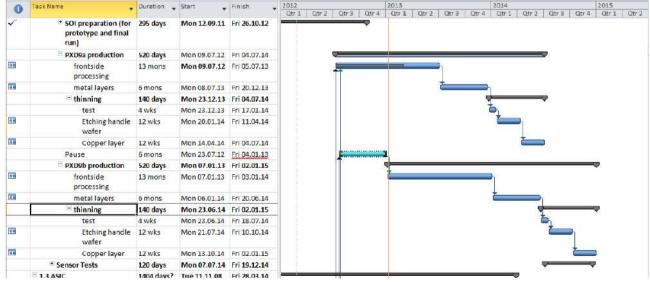

#### **DEPFET Production**

First production batch with 13 wafers started in HLL in July

•one wafer has sensors for 1 inner and 2 outer ladders

Nominal processing time (including thinning): 2 years

Processing runs smoothly, ahead of schedule

Second batch with 18 wafers will follow soon

Yield requirements:

20% for outer layer 27% for inner layer

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

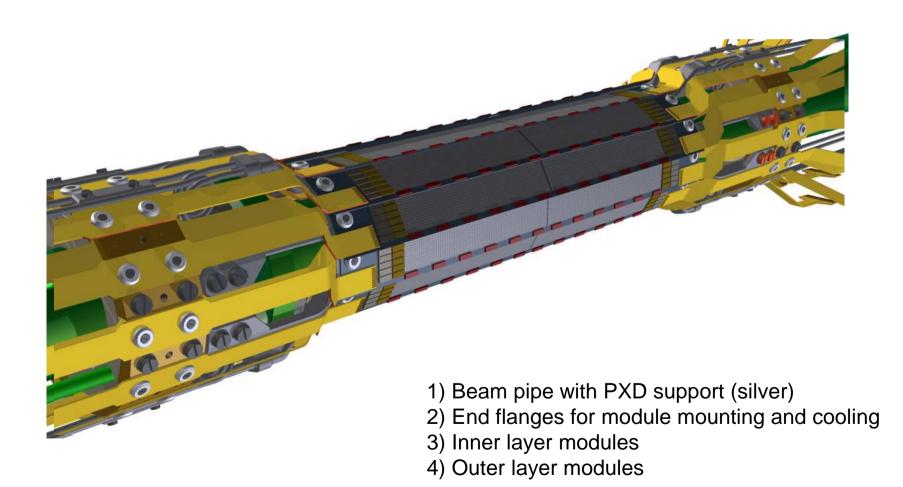

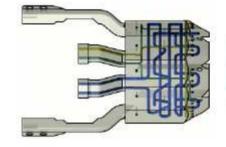

# End Flange - Cooling Block

- Cooling system outside acceptance

- Closed CO2 cooling system for readout electronics (320W)

- Cold dry air for steering chips and DEPFET pixels (40W)

150mW/cm<sup>2</sup>

•Stainless steel •Fast sintering •Blue: CO2 channels •Yellow: Air channels

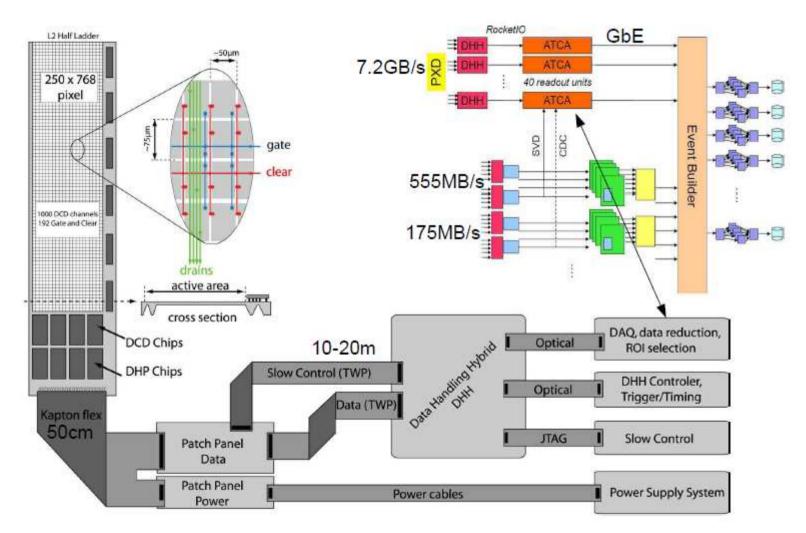

Max data rate: 20 GB/s @ 3% occupancy (expected: 0.8%) Date reduction (ROI selection): ~ 700 MB/s

SuperKEKB upgrade progressing well

-> machine commissioning starts beginning of 2015

#### Major upgrade of Belle II detector underway (inner detector, PID, KLM)

#### **Pixel Detector:**

- DEPFET sensors thinned to 75µm

- low mass self supporting, air cooled module: 0.21% X0

- S/N, resolution, readout speed and radiation hardness tested

- production of final sensors started

- CO<sub>2</sub> cooling for ASICs (and SVD)

- mounting blocks with integrated cooling channels (3D printing)

Installation of PXD/SVD: September 2015

Physics start: mid 2016

J. Kemmer and G. Lutz, "New semiconductor concept, " NIM A 1987

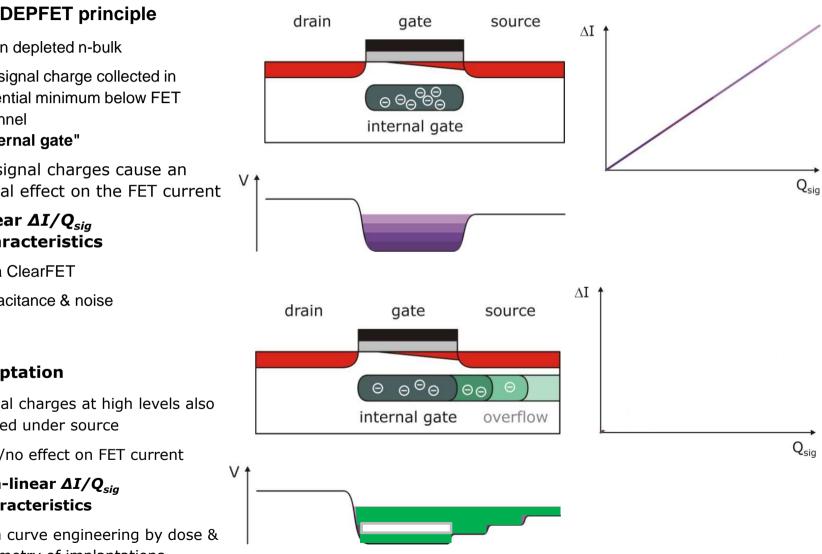

p-FET on depleted n-bulk 0

6. Do>+

- → All signal charge collected in potential minimum below FET channel "internal gate"

- $\rightarrow$  all signal charges cause an equal effect on the FET current

- $\mapsto$  linear  $\Delta I/Q_{sig}$ characteristics

- reset via ClearFET 0

- low capacitance & noise 0

#### **DSSC** adaptation

- → signal charges at high levels also stored under source

- less/no effect on FET current  $\rightarrow$

- $\rightarrow$  non-linear  $\Delta I/Q_{sig}$ characteristics

- $\rightarrow$  gain curve engineering by dose & geometry of implantations

#### Need O(100x) more data →Next generation B-factories

H.-G. Moser, Joint Instrumentaton Seminar, Hamburg, Jan. 18, 2013

p. Dg> th