# Front end electronics and FPGA developments

#### **Patrick Gessler**

for the Joint Electronics Group Detector Developments (WP75) + Data Acquisition (WP76) European XFEL GmbH

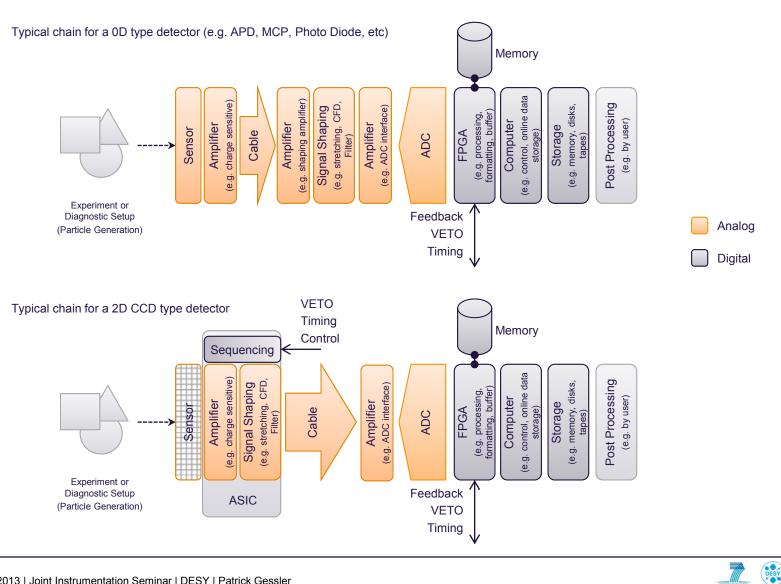

#### **XFEL** Overview

- Front end electronics

- Overview of typical Detector-Data-Acquisition Chains

- Usual tasks and pitfalls depending on detector and detection principle

- Introduction into MicroTCA as data acquisition platform

- Motivation

- Overview

- FPGA developments

- Brief introduction into FPGAs

- Main tasks and required features

- Programming principles followed

- High-Level Algorithm Programming Framework with Simulink

- High-Speed and Low-Latency Serial Interfaces

- High resolution trigger

- Pulse energy detection

- Conclusion

A

HELMHOLTZ ASSOCIATION

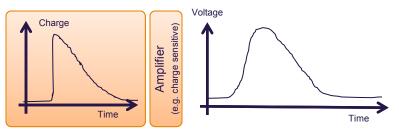

Convert collected charge into voltage or current

- The bandwidth of the amplifier could be lower than the one of the sensor (like in the example)

- Charges are collected and formed in a current

- The amplifier produces a proportional output voltage

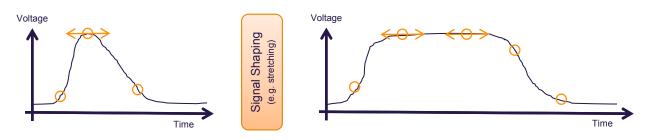

- Pulse stretching

- To sample all important properties with limited sampling speed

- To reduce noise by oversampling and later averaging

- To reduce jitter based effects (sampling time fluctuations)

- Negative:

- Fast signal properties are lost

- Time between pulses has to be longer

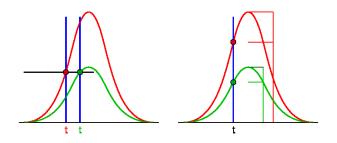

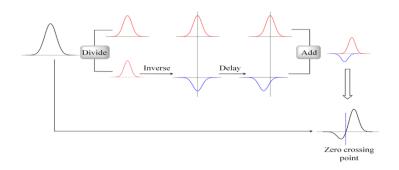

- Constant Fraction Discrimination (e.g. for ToF experiments)

- Using a threshold for time determination provides an error

Amplitude independent time detection by constant fraction

Divider and time delay are usually user parameters!

Pictures from wikipedia

#### **European** Front end electronics:

Typical tasks depending on detector and detection principle

- Low pass filtering

- Def.: All frequency components UP TO the cut-off frequency will pass

- The cut-off is the 3dB line → this means higher frequencies are only attenuated!

- The order of the filter defines the "sharpness" of the cut-off

- Applications

- Reduce high frequency noise

- Match signal bandwidth to ADC sampling rate or input bandwidth

- To avoid signal reflections and imaging effects in the data

#### **European** Front end electronics:

L Typical tasks depending on detector and detection principle

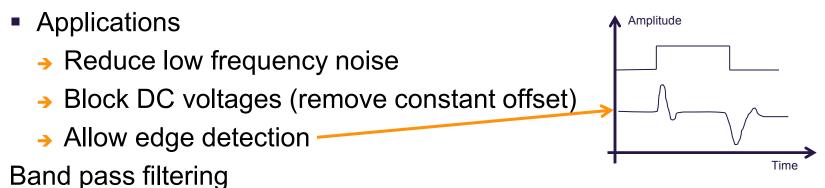

- High pass filtering

- Def.: All frequency components ABOVE the cut-off frequency will pass

- The cut-off is the 3dB line → this means lower frequencies are only attenuated!

- The order of the filter defines the "sharpness" of the cut-off

- Combines low and high pass and provide two cut-off frequencies

- Notch filter

- Is the inverse of the band pass filter

#### European XFEL

#### Front end electronics:

L Typical tasks depending on detector and detection principle

- AC and DC input coupling to ADCs

- AC: Alternating Current

- Used for alternating (usually periodic) signals

- Includes high-pass filter to block DC voltages!

- Be aware of high-pass filter effects like fluctuating base line

- Positive: Usually only passive connection (capacitor)

- DC: Direct Current

- Used for arbitrary signals

- Usually includes an amplifier (increases noise and limits bandwidth)

- Due to the amplifier mostly low-pass filter behavior

- Positive: constant base line (no drifts)

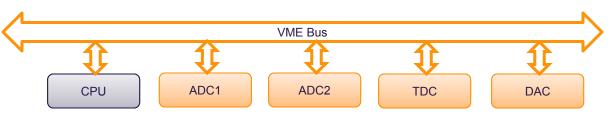

### **XFEL** Introduction into MicroTCA – Motivation

- Limitations on existing VME based solutions

- Bandwidth: only one parallel bus

- No module replacement at run time (Hotswap)

- Remote control

- Health management

- Redundancy

- No in-crate timing distribution

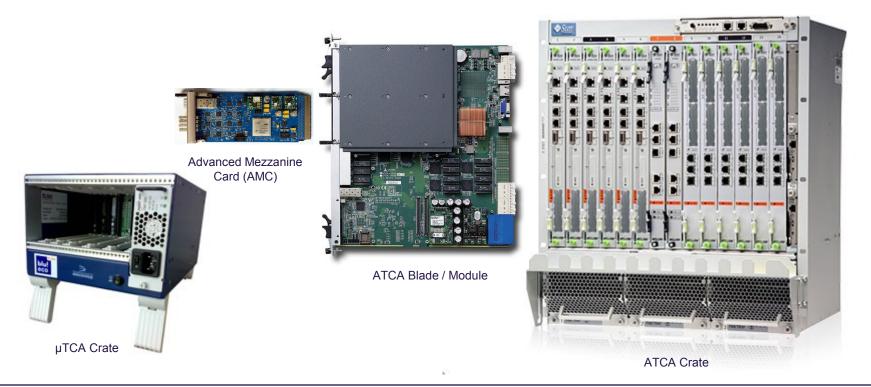

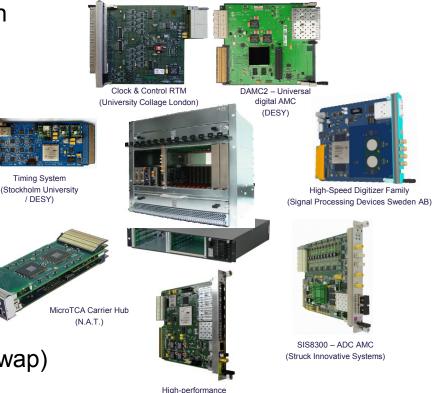

#### **XFEL** Introduction into MicroTCA – ATCA and MTCA

- Advanced Telecommunication Computing Architecture (ATCA)

- Advanced Mezzanine Card (AMC)

- Micro Telecommunication Computing Architecture (µTCA)

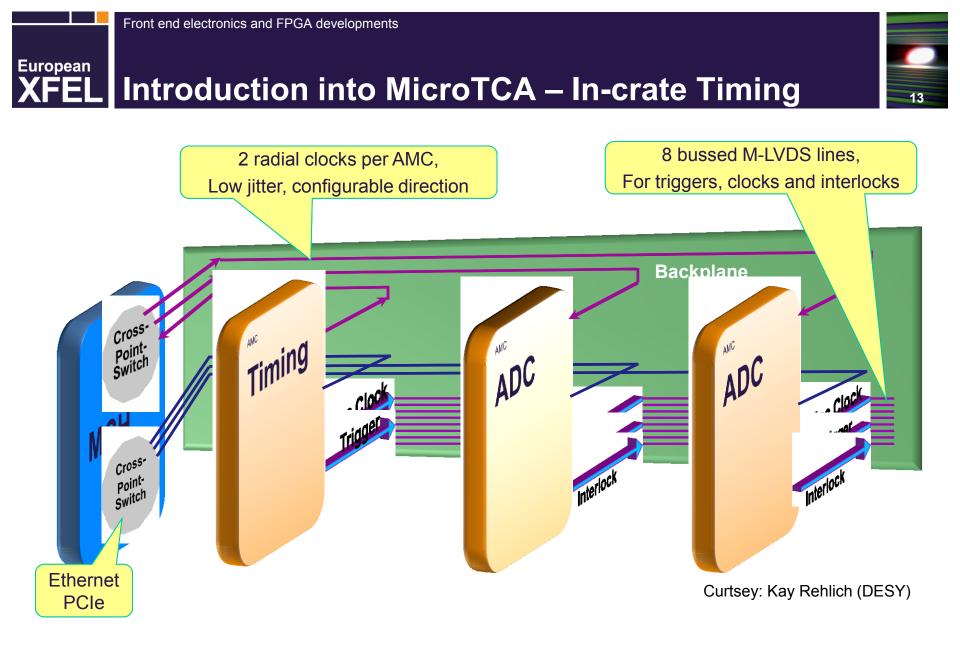

#### **XFEL** Introduction into MicroTCA – MicroTCA.4

- xTCA not designed for physics applications (e.g. Timing, Interfacing, ADCs)

- xTCA for Physics Group at PCI Industrial Computing Manufacturers Group (PICMG)

- Participants from labs and industries

- Defined extensions of the standard for our applications

- Timing interface on the backplane

- High-speed module interconnections

- → More space → double size modules

- → Modular interfacing and signal shaping → Rear Transition Modules (RTMs)

DESY DAMC1

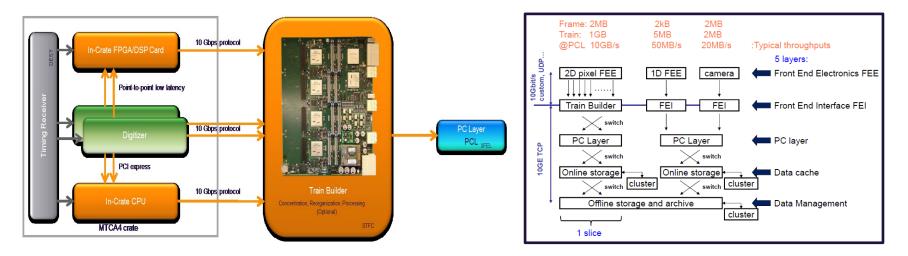

#### **XFEL** Introduction into MicroTCA – as main platform

MicroTCA.4 allows

European

- High-bandwidth communication between

- Boards and CPU via PCIe

- Boards via point-to-point connections

- Synchronization via Timing Receiver

- Trigger

- Clocks

- Machine parameters

- Bunch structure

- Remote control and monitoring

- Module changes during operation (Hotswap)

- Functional extension via RTMs

If you are interested in this topic, please register for the MicroTCA Workshop in December @ DESY: http://mtcaws.desy.de

DSP and FPGA board (DMCS/DESY)

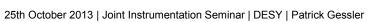

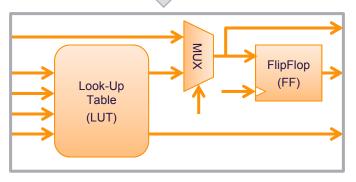

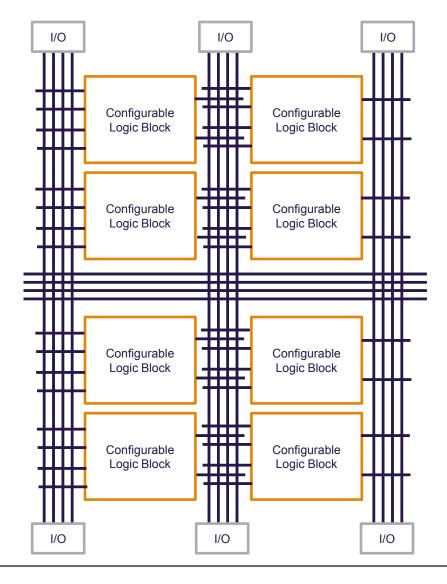

#### **XFEL** Brief introduction into FPGAs

- Field Programmable Gate Array (FPGA)

- Allow hundreds of thousand logic functions

- All in parallel (if required)

- Reprogrammable by the user

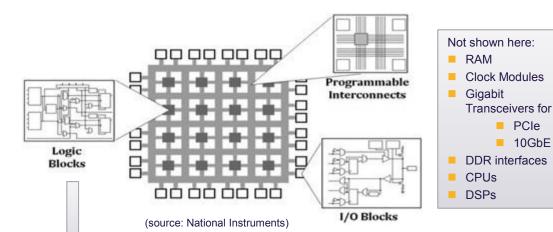

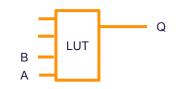

Simplified Configurable Logic Block (CLB)

"Only" 665 pins. Largest one has 1760 pins (source: Xilinx)

## **XFEL** Brief introduction into FPGAs

- Field Programmable Gate Array (FPGA)

- Flexible inner structure

Simplified Configurable Logic Block (CLB)

| Α | В | AND | OR | NAND | XOR |

|---|---|-----|----|------|-----|

| 0 | 0 | 0   | 0  | 1    | 0   |

| 0 | 1 | 0   | 1  | 1    | 1   |

| 1 | 0 | 0   | 1  | 1    | 1   |

| 1 | 1 | 1   | 1  | 0    | 0   |

Look-Up Table (LUT) examples with 2 inputs only

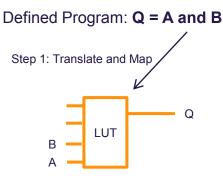

#### **XFEL** Brief Introduction into FPGAs - Example

Defined Program: Q = A and B

#### **XFEL** Brief Introduction into FPGAs - Example

European

FEI

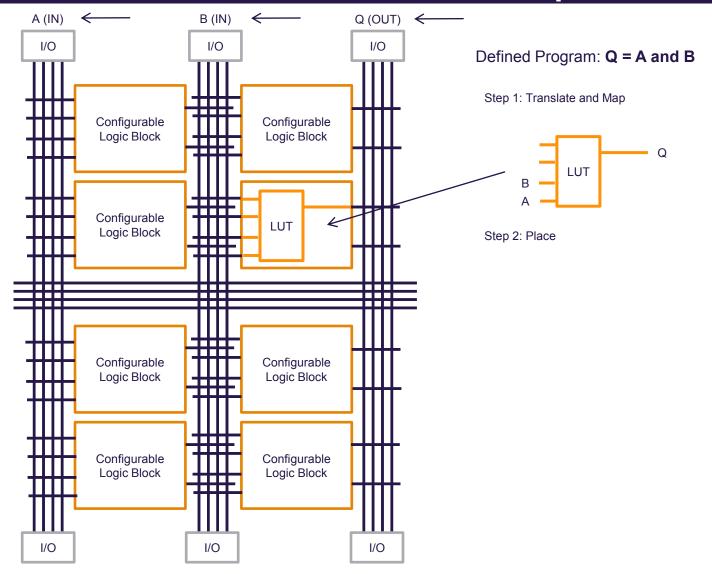

## Brief Introduction into FPGAs - Example

European

**H**

20

#### A (IN) B (IN) Q (OUT) I/O I/O I/O Configurable Configurable Logic Block Logic Block ╋╋╋ Configurable LUT Logic Block Configurable Configurable Logic Block Logic Block Configurable Configurable Logic Block Logic Block ╋╋╋ I/O I/O I/O

**Brief Introduction into FPGAs - Example**

Defined Program: Q = A and B

Step 1: Translate and Map

Step 2: Place Step 3: Route

## **XFEL** Main tasks and required features of FPGAs

- Receive data from

- Integrated circuits (e.g. ADCs)

- Other modules via communication interfaces

- Synchronize data flow (Triggers, clocks)

- Online) Processing of data (with run-time parameters)

- Iike integration, peak detection, TDC, FFT, etc

- (Re-)Formatting and coding of data

- Iike 10Gb Ethernet

- Transmission of data (e.g. high-bandwidth, low-latency)

- Monitoring, debugging and diagnostics

Front end electronics and FPGA developments

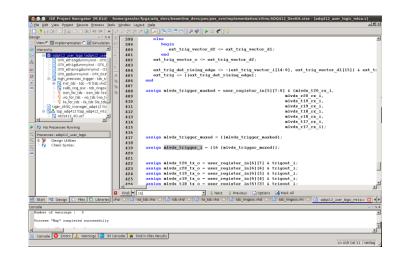

```

entity myAND is

port( A: in std logic;

B: in std logic;

Q: out std logic

);

end myAND;

architecture RTL of myAND is

begin

O \ll A and B;

end;

```

Xilinx ISE is one tool for VHDL Programming for the FPGA

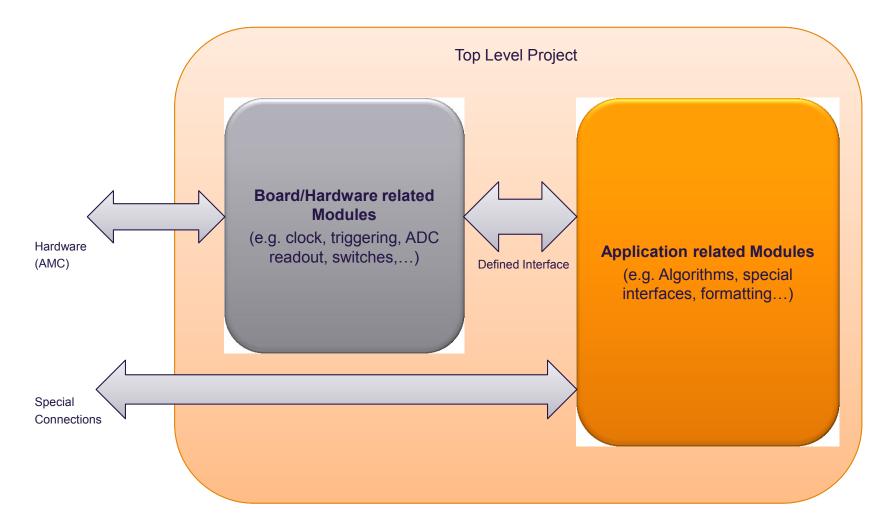

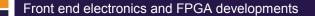

### **XFEL** Providing Structure: Start-Up Projects

#### **XFEL** Providing Structure: Start-Up Projects

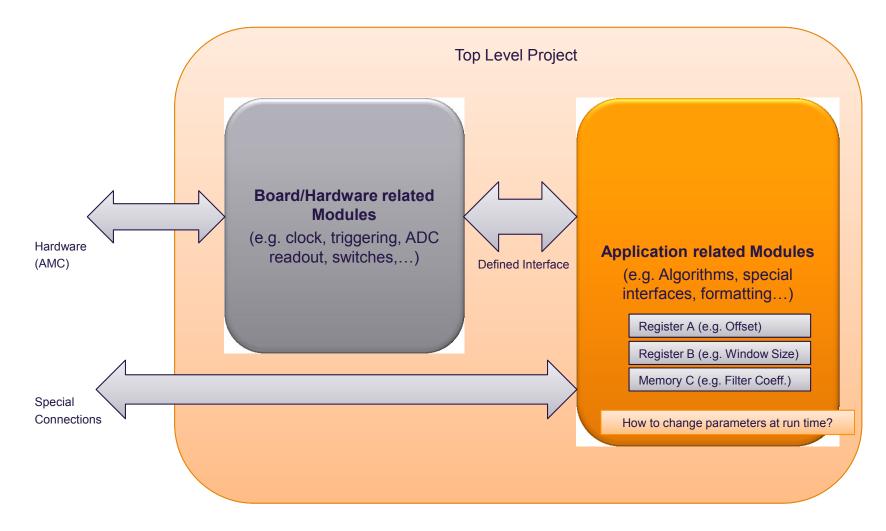

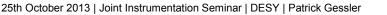

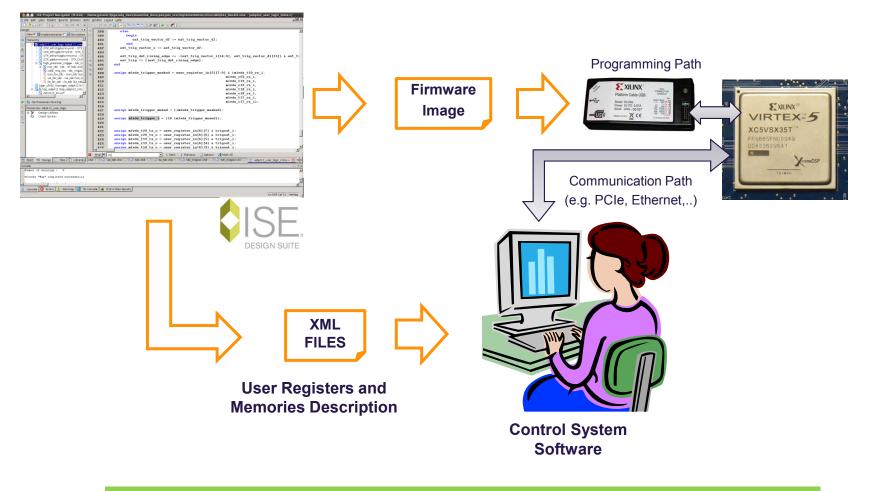

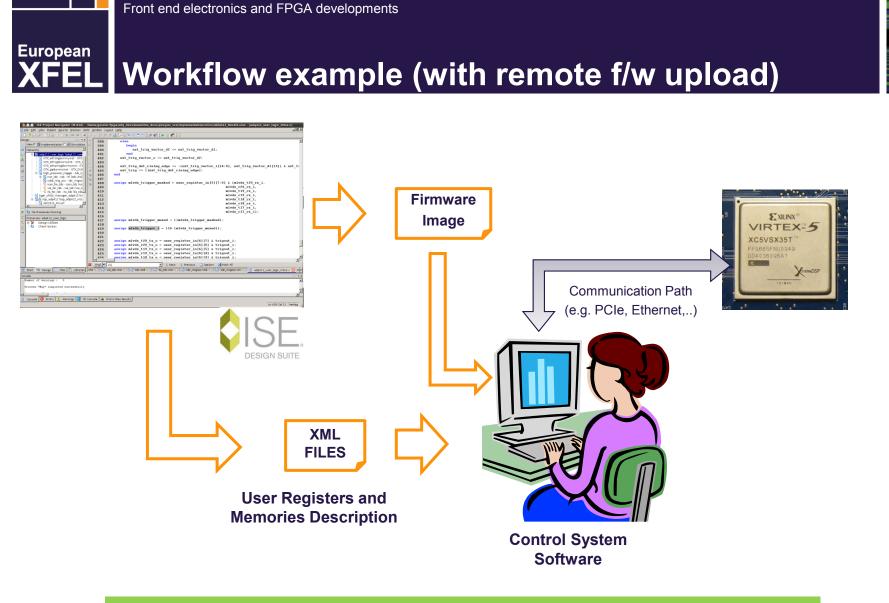

#### European Providing Computer Connection: PCIe / II Bus XFEL

This system allows automatic detection of installed firmware and loads correct XML files with Register und Memory descriptions

25th October 2013 | Joint Instrumentation Seminar | DESY | Patrick Gessler

It also allows centralized remote firmware management (e.g. version tracking and remote upload synchronized with s/w updates)

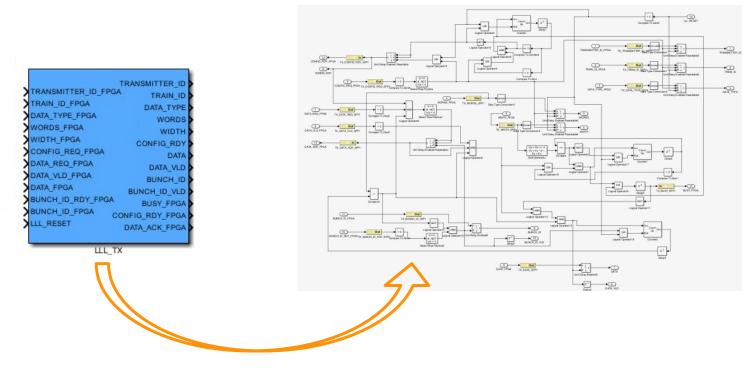

#### **XFEL** High Level FPGA Algorithm Development

The FPGA should bend time and space according to  $R_{\mu\nu} - \frac{1}{2}R g_{\mu\nu} + \Lambda g_{\mu\nu} = \frac{8\pi G}{c^4} T_{\mu\nu}$

- FPGA programming is time intensive and requires specialists, however most applications and algorithms are conceptualized by users unfamiliar with FPGA programming.

- For the European XFEL, a high level FPGA framework is being developed that allows for users with no prior HDL knowledge to develop their algorithm modules which can be integrated in a top VHDL project.

## **XFEL** High Level FPGA Algorithm Development

- The Framework should:

- Abstract end user from hardware programming languages and concepts such as Pin placement, clock routing, etc.

- User design environment automatically setup for the target board;

- Library with blocks that simulate the behavior of available features;

- User defined registers and memories and generate the necessary logic to later communicate with the bus protocol;

- Easy to port and distribute applications to other projects/boards.

#### **XFEL** XFEL Simulink Library – Project Definitions

|                        |             | Block Parameters: Project Definitions             | ×  |

|------------------------|-------------|---------------------------------------------------|----|

| European               | System      | - Subsystem (mask) (link)                         |    |

| XFEL<br>iect Definitio | Generator   | Parameters                                        |    |

|                        |             | Board Project SIS8300 -                           |    |

| In<br>ESET             | AD C9       | Board Version 0                                   |    |

| Out                    |             | Bus type Internal Interface (II)                  |    |

| EDS                    | ADC10       | Major Version                                     |    |

| In 🕨                   | > In >      | 1                                                 |    |

| ADC1                   | TRIGGER     | Minor Version                                     |    |

| In 🕨                   | > In >      | 3                                                 |    |

| ADC2                   | EXT_TRIGGER | Reintroduce Missing IO                            |    |

| In<br>ADC3             |             | E Do not generate Bus                             | 4  |

| In ADC4                | LLL_RESET   | <u>Q</u> K <u>C</u> ancel <u>H</u> elp <u>App</u> | ly |

- The Project Definitions block: the user defines for which board the algorithm is going to be develop as well as the bus protocol:

- Generate the IO available for the chosen board and examples of expected input signals;

- Includes the System generator block and defines its parameters according to the FPGA board.

## **XFEL** XFEL Simulink Library – BUS Block

BUS block allows for users to define registers and memories which are later accessible by the chosen protocol

|     | Input Register Example                   | Vector of Input<br>Registers Example | In_1 Out_1<br>In_2 Out_2<br>Multiple Input<br>Registers Example |

|-----|------------------------------------------|--------------------------------------|-----------------------------------------------------------------|

| BUS | Output Register Example                  | Multiple Output<br>Registers Example |                                                                 |

|     | Addr<br>Din Dout<br>Wr<br>Memory Example |                                      |                                                                 |

| 3           | Function Block Parameters: BUS                      | ×     |

|-------------|-----------------------------------------------------|-------|

| Subsystem   | (mask) (link)                                       |       |

| Parameters  | ;                                                   |       |

| Name        |                                                     |       |

| Input Regi  | ster Example                                        |       |

| Type Regi   | ster 🔹                                              |       |

| Direction   | Input 🔹                                             |       |

| Data Type   | Fixed-point 💌                                       |       |

| Data Arith  | Unsigned 🗸                                          | 11111 |

| Number of   | Bits                                                |       |

| 16          |                                                     |       |

| Number of   | Frac. Bits                                          |       |

| 3           |                                                     |       |

| Vector Nun  | nber                                                |       |

| 1           |                                                     |       |

| Input is '  | Vector                                              |       |

| Description | 1                                                   |       |

| This is an  | example of a 16 bit wide user register.             |       |

|             |                                                     |       |

|             | <u>OK</u> <u>C</u> ancel <u>H</u> elp <u>A</u> pply |       |

#### **XFEL** XFEL Simulink Library – Board Specific block

- Specific blocks are available on the library which will accurately simulate the behavior of features available on the board;

- In Hardware, the block is replaced with the real implementation.

## 33

#### European **XFEL Simulink Library – Application Integration User Application** ) In Standalone Module of Systen > In AddSub **User Application** and Logical **XML User Registers and** Software FILE **Memories Description Karabo** Relationa NGC FILE bus\_mod DESIGN SUITE **Final Design Bus protocol logic** generated automatically

- The final Algorithm is processed to integrate the top level FPGA Project:

- Generate Final Design with bus interface logic <u>based on defined user registers</u> and chosen protocol;

- Netlist file of final design inserted in ISE project;

- Standalone Module of User application to share and distribute

- XML file with register information similar to the VHDL developed applications.

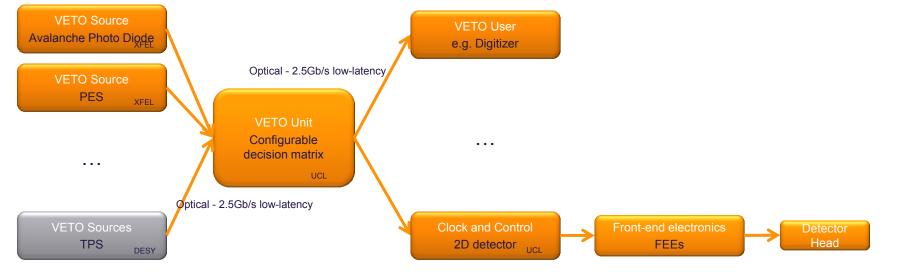

## EuropeanLow-Latency data transmission:XFELVETO System for data reduction and memory optimization

- Optimize picture quality of 2D detectors

- Limited frame capacity in ASICs (~300-700 frames)

- Replace bad frames with new ones in ASIC before read out and transmission

- Data reduction

- Discard useless data before transmission

- Implementation

- FPGAs of diagnostics and detectors provide bunch information with low-latency

- Configurable central VETO unit per experiment decides on bunch quality

- FPGAs of detectors (maybe also diagnostics) receive the decision and react on it

- Using a common protocol with beam based feedback system

Front end electronics and FPGA developments

## European I

#### High-Bandwidth data transmission 10Gb Ethernet data streaming

#### Driving force: fast and large area detectors

| Detector type       | Sampling | Data/pulse | Data/train | XFEL/sec | LCLS/sec |

|---------------------|----------|------------|------------|----------|----------|

| 1 Mpxl 2D camera    | 4.5 MHz  | ~2 MB      | ~1 GB      | ~10 GB   | ~300 MB  |

| 1 channel digitizer | 5 GS/s   | ~2 kB      | ~6 MB      | ~60 MB   | ~0.2 MB  |

#### Chosen architecture:

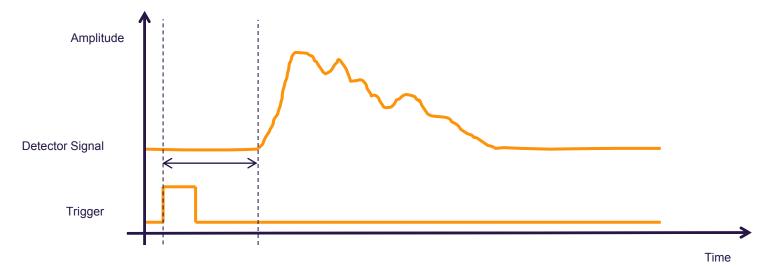

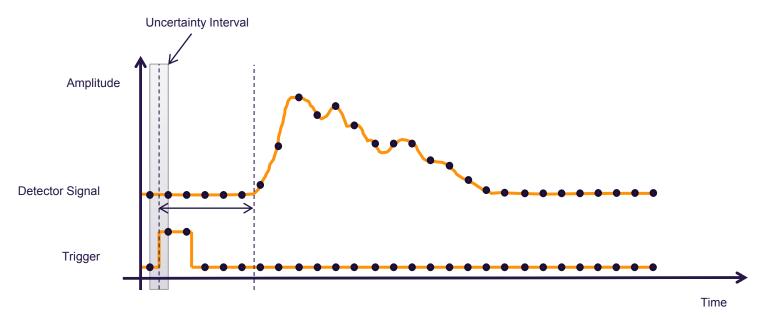

- Triggering Basics:

- "A trigger defines the point in time relative to an event (e.g. detector signal) to be observed"

The trigger is used to start data acquisition and processing

## **XFEL** High Resolution Trigger

- In the digital world:

- Signal and trigger are quantized in discrete time steps

The trigger time is only known at the step size of the sampling time of the trigger

Comment: If the trigger has a constant time to the following sampling clock edge and therefore also to the signal, the problem is not there anymore.

HELMHOLTZ

ASSOCIATION

## **XFEL** High Resolution Trigger

- In many applications the signal sampling clock is much higher than the trigger sampling clock (factor > 8)

- In this case the uncertainty is higher than the signal sampling accuracy!

- Solutions:

- Synchronize clock sampling phase to experiments reference

- Not always possible (due to internal PLLs)

- Increases noise through external clock

- Increase sampling speed for trigger

- Jusual maximum in FPGAs: between 1 and 2.5 GBPS

- Jsing Time-to-Digitial converter (TDC) technology

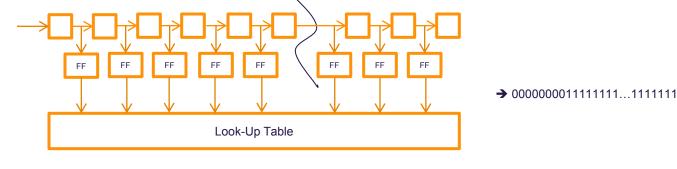

## XFEL High Resolution Trigger

- Different TDC implementations in FPGA possible

- The currently under implementation at XFEL:

- Using logic propagation delays

**→** 15

#### Challenges:

- complicated timing relations in FPGA

- Calibration and temperature induced drift compensation

- Expected resolution: down to 50ps

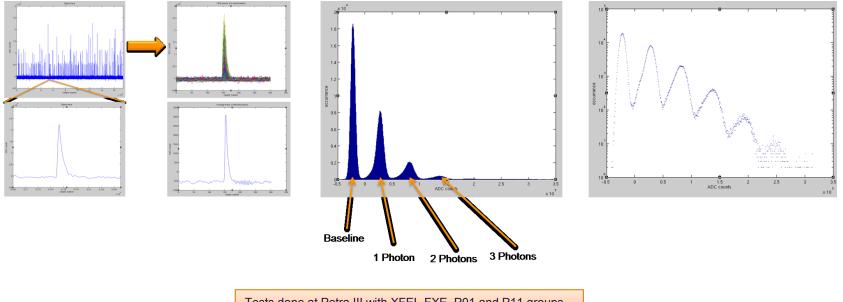

## **XFEL** Pulse Energy Detetction

- Different possibilities tested

- Integration (summing of samples) and

- Cross-Correlation (Matched filtering)

Tests done at Petra III with XFEL FXE, P01 and P11 groups

### XFEL Conclusion

- Analog front end electronics are required in order to

- Convert the charges of a sensor to be detected

- Shape the signal for the digitalization process

- Amplify and filter the signal to optimize signal-to-noise ratio

- A transition from VME to MicroTCA for the XFEL.EU was required

- To increase the availability (reduce downtime)

- Allow for higher data bandwidths for faster digitizers and detectors

- The development of FPGAs

- Allows for high flexibility and also includes high complexity

- Many effort had been done on simplify the work to

- Speed up the development time

- Reduce errors

- Improve maintainability

- Key algorithms are under development or test

- Non experienced people can do FPGA programming in Simulink